研究内容

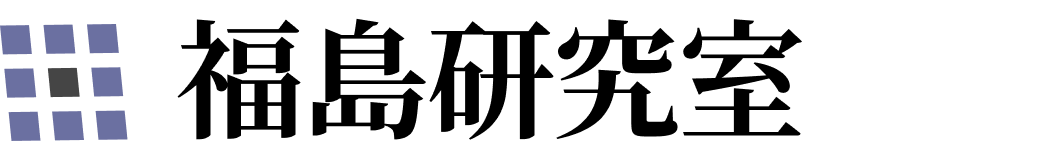

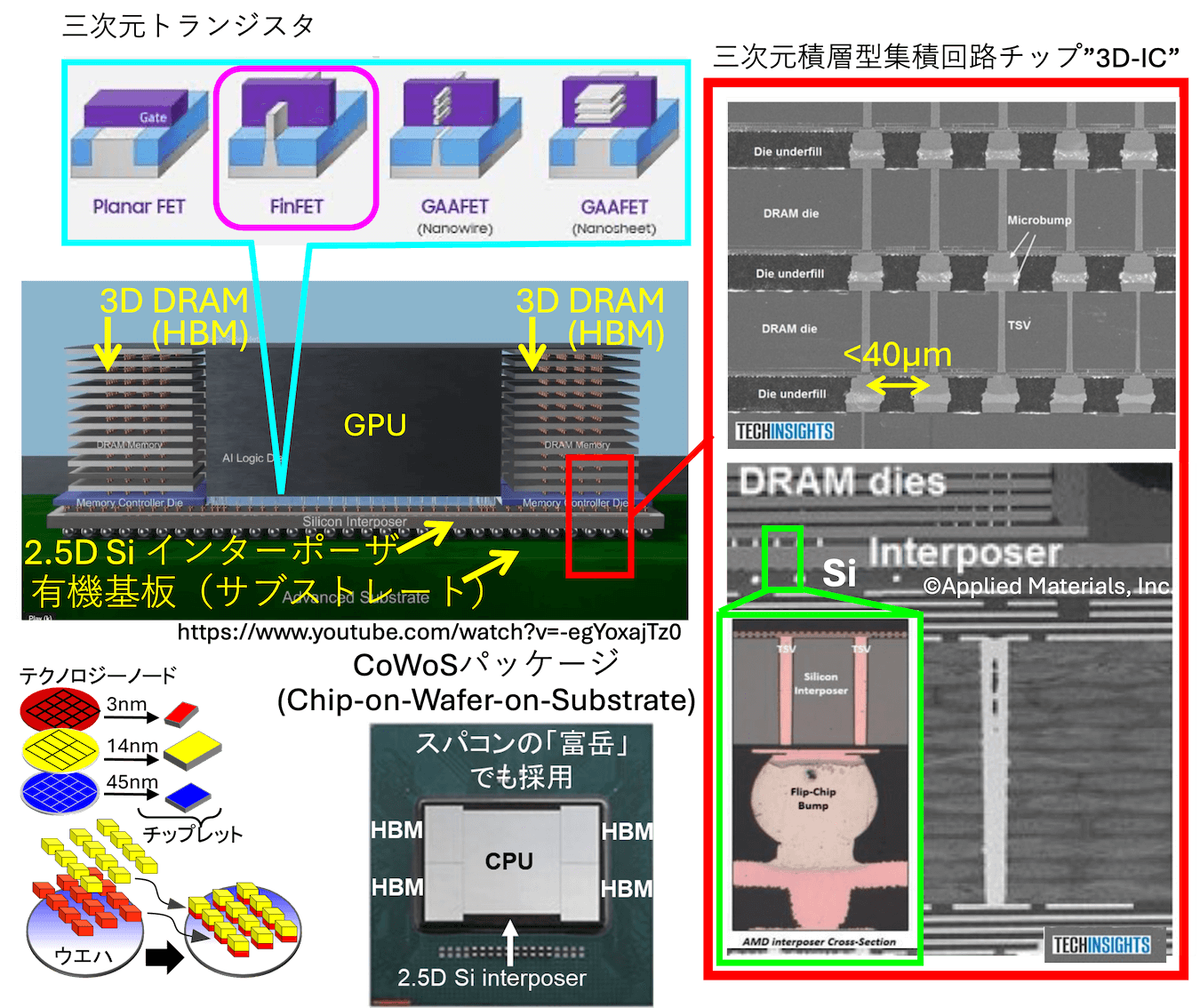

平屋で足りなくなれば二階建て、それでも足りなくなれば高層マンション。広大な駐車場が無ければ、狭い空間でも多くの車を駐車できるように立体駐車場。このように日常でも三次元化する動きはごく自然に受け入れられてきました。集積回路では、トランジスタの三次元化とともに、チップそのものを三次元積層構造にする研究も進められています。しかし、どうやって縦に積んだチップ間のインターコネクションを実現するのか?三次元化することで厚みが増えたり、より電力を消費するようなチップはこの業界では受け入れられません。この課題に挑戦し、ブレークスルーを引き起こしたのが東北大学の我々の研究室の前身です。30年以上前(1995年〜)の話です。

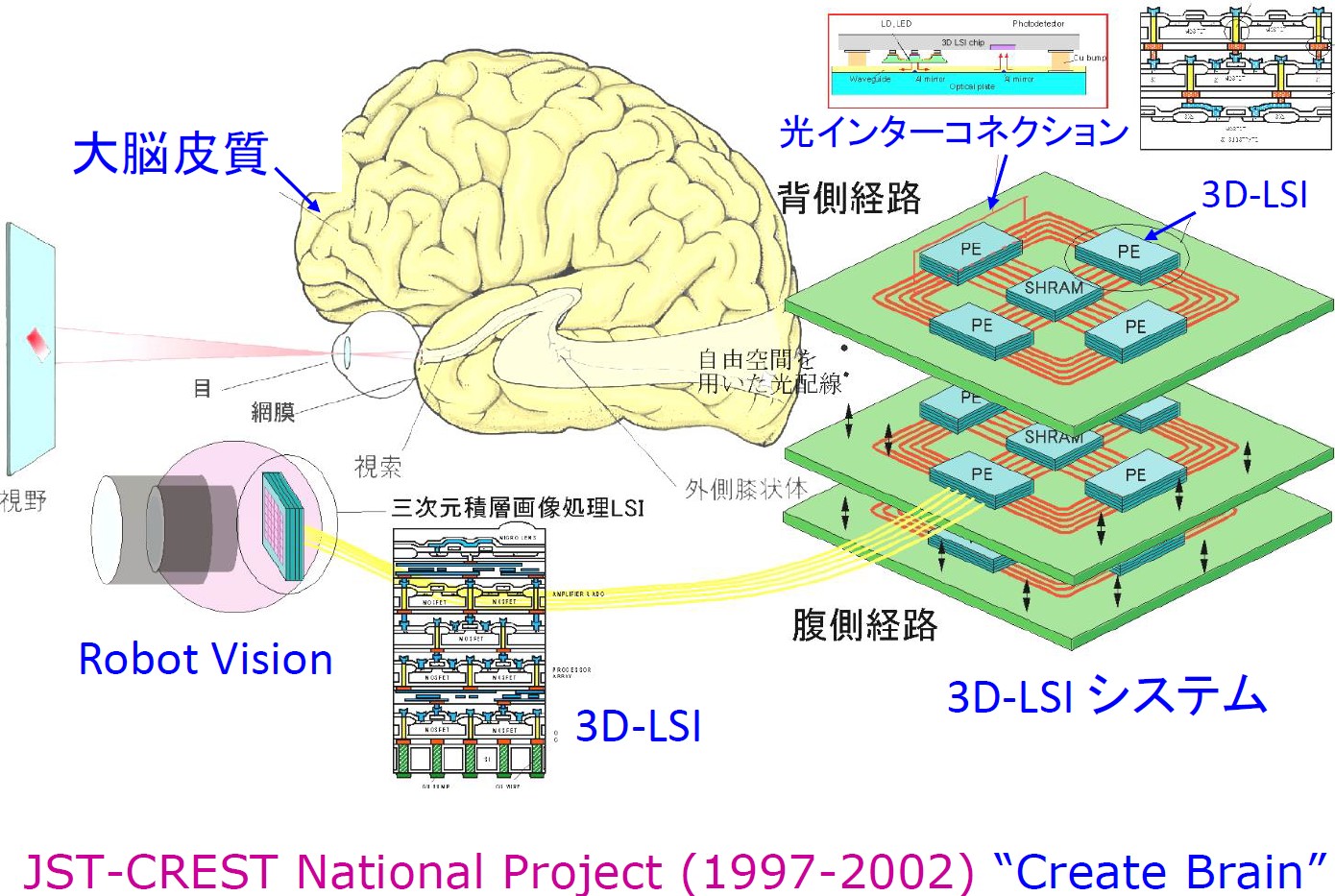

シリコン貫通配線(TSV: Through-Silicon Via)と呼ばれる技術は、チップの母材である単結晶Siを貫通させ、チップ自体を薄化して僅か数10µmとし(通常の直径300mmのSiウエハの厚さは775µm)、これを貫通する非常に微細で短い垂直配線(直径数µm)を作って、上下のチップ間の電気的な接続を可能にします。この技術は、最近、皆さんの周りでよく使われるようになった生成AI、特に米国NVIDIA社が設計し、台湾TSMC社で製造されるGPUモジュールの基幹となる大容量メモリHBM(High-Bandwidth Memory)や、スパコン富岳でも採用されているSiインターポーザ(CPUとHBMを接続するための高速信号伝送用の中継基板)でも用いられています。ちなみに、HBMの原型となる三次元積層型のDRAMを世界で初めて発表したのも当研究室の系統の出身者です。2000年に世界最高峰の半導体デバイス技術に関する国際会議IEDMで発表されました。

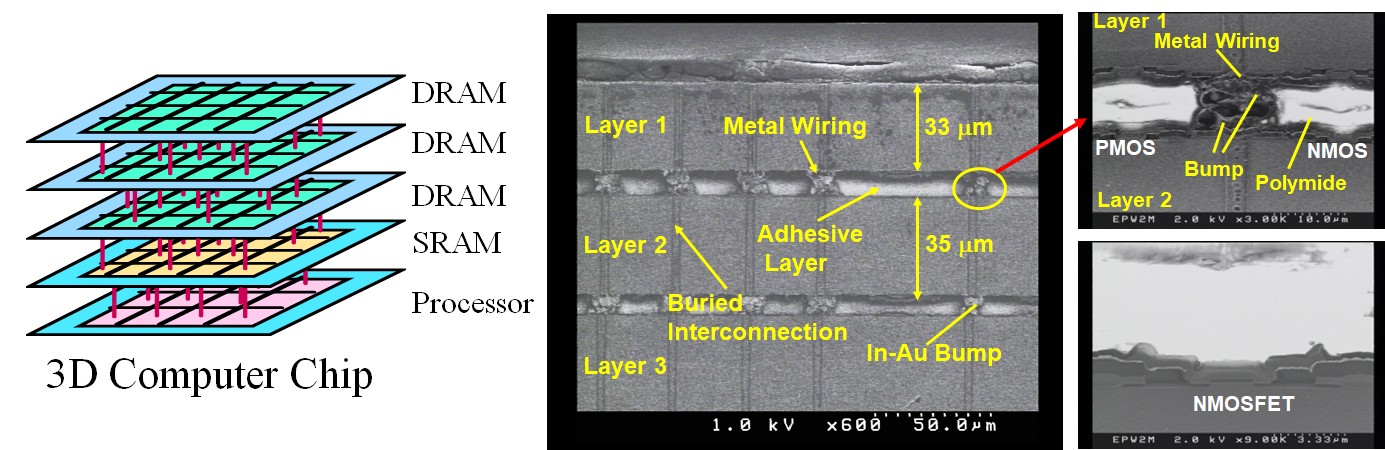

当研究室の代表である福島の貢献はChip-to-Wafer三次元集積という技術です。2005年のIEDMで世界に先駆けてこの技術の有用性を実証しています。いまではこの技術が生成AIを構成するGPUモジュールを集積するための基盤技術であると言っても過言ではありません。このように当研究室の強みは三次元積層型集積回路チップ(3D-IC)を作製するためのプロセス技術・材料技術です。この新しい集積回路の集積化形態を生み出すのに必要な種々のマイクロ・ナノ加工工学や半導体パッケージング工学に関する研究に注力してきました。

しかしながら、いまだに3D-ICは、一部の垂直統合型企業でしか製造することができず、高コストと言われており、3D-ICの民主化が遅れています。この問題を解決すべく、我々は従来の平たい二次元の集積回路(2D-IC)を三次元化する新技術を研究しています。既に出来上がった2D-ICを当研究室に持ち込めば、チップをダイレベルで薄化してTSVを形成し、三次元積層に必要とされる微小な半田のマイクロバンプを作って接合させ、新しい3D-ICを創出させます。さらに膨大な情報量をともなって加速する本格的なAI社会に適用できる3D-IC作りに取り組んでいます。

モノづくり研究に興味がある方は、世界に伍する微細加工施設(クリーンルーム)を有する当研究室で一緒に新世代の3D-ICを創製してみましょう。学生時代でしか経験できない自由で柔軟な半導体微細加工と集積化の研究に魅せられると信じています。直径300mmのSiウエハを扱える製造装置群を有する研究室は世界でも非常に稀です。是非、この貴重な経験を通して、理論的な考え方を育み、日本の半導体復興に挑戦しましょう。

NVIDIAが設計し、TSMCで製造されるGPUモジュールが、生成AI向けのAI半導体として注目。

このGPUモジュールの基幹デバイス構造は、当研究室から発信された技術の終結。

世界で我々だけのチップレベルで3D-ICを作製する技術を構築

3D-ICを作製するための主要素技術の一つがTSVであることは疑いの余地がありません。しかし、TSVだけでは3D-ICを作製することはできません。以下の技術が組み合わさって初めて3D-ICは完成します。

- ウエハやチップの薄化技術(研削・研磨)

- ウエハやチップの高精度位置合わせ技術

- 半田の微細マイクロバンプ形成技術

- ウエハやチップの低温接合技術

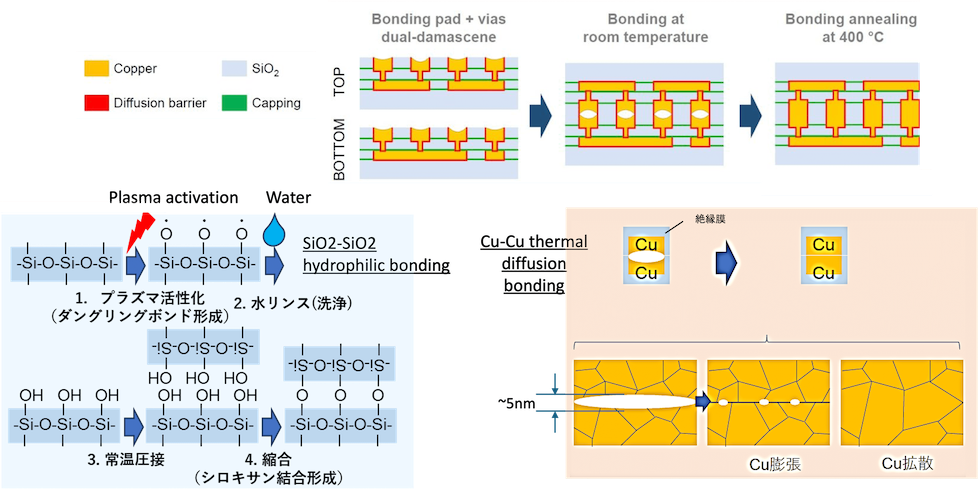

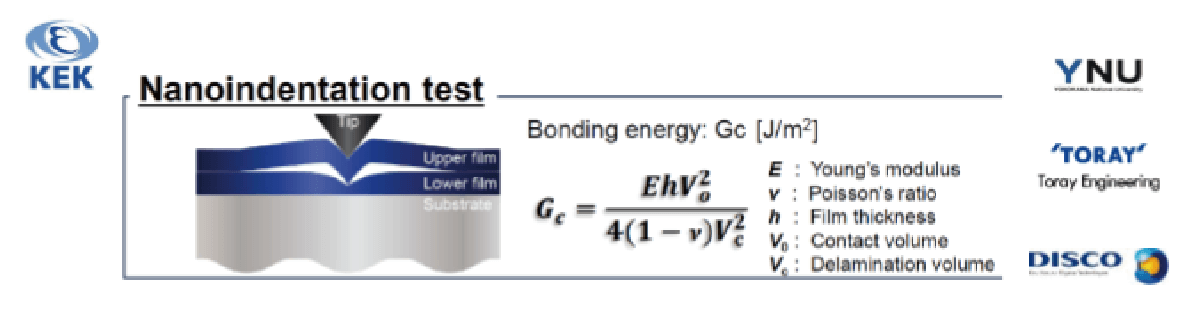

我々はこれらの要素技術全ての研究に取り組みながら3D-ICの研究開発を進めてきました。最近、注目されているのが「ハイブリッド接合」技術です。これまでは半田の微細マイクロバンプ電極をめっきで形成し、その半田を熱圧着してウエハ間、チップ間を電気的に接続していました。しかし、半田のマイクロバンプ電極は、250℃ほどの高温で押しつぶすと、潰れて横に広がるスクィーズと呼ばれる現象が起き、隣り合う電極間でショート(電気的な短絡)を引き起こします。また、半田マイクロバンプで接合した後のウエハ間、チップ間には20µmほどの間隙ができるため、そこにはアンダーフィルと呼ばれる樹脂を毛管力等で注入しなければ機械的な信頼性が得られません。この間隙も年々狭くなってきており、アンダーフィルの限界も囁かれています。したがって、量産技術でも半田を使った接合では、電極ピッチ30µmまでしか微細化が達成できていません。

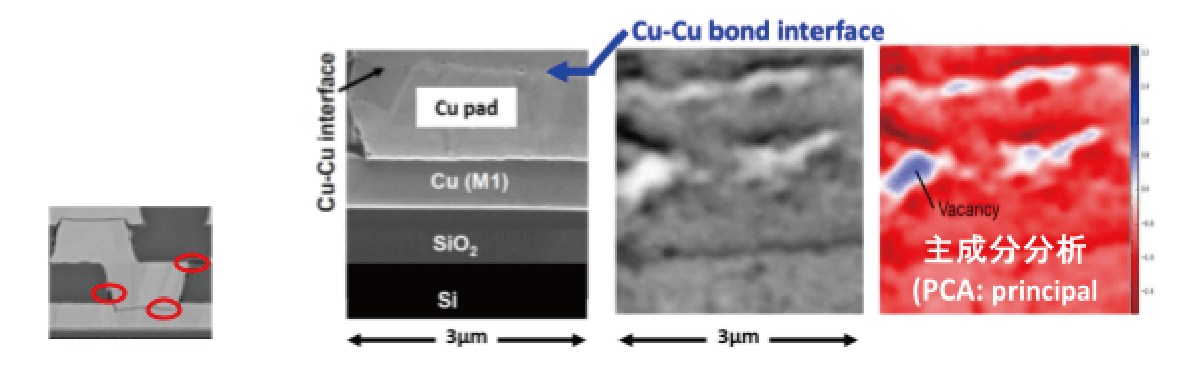

ハイブリッド接合は、Cu(銅)とCuを半田レスで接合する技術であると同時に、Cu電極を囲うSiO2系の絶縁膜も同時に原子レベルで接合する技術です。Cu-Cu/SiO2-SiO2を同時に接合する、まさにハイブリッドな接合です。バンプ電極を使わずにCu面とSiO2面を平坦化して接合するので、アンダーフィルは必要ありません。しかし、半田と違って溶融しないため、固相状態でCuとSiO2の表面をプラズマで活性化する必要があります。また、原子レベルで平坦化しなければ理想的な接合は成り立たず、接合温度も400℃近い高温を必要とします。微小なゴミ(半導体の世界ではパーティクルと呼ぶ)があるとチップ自体が十分に高い強度で接合しなくなるので、クリーン度の管理も非常に重要です。次世代の接合技術として注目されていますが、実は皆さんのスマホのCMOSイメージセンサと呼ばれるカメラモジュールでは2層構造品が、2016年以降から量産されています。2層構造のTSVを含まない技術に比べ、TSVを含めた3層以上のハイブリッド接合では技術レベルの次元が異なり、2025年現在、世界中で技術開発が盛んに行われています。

世界最大の半導体パッケージング技術に関する国際会議ECTCでこのハイブリッド接合に関する研究が多数報告されています。ECTC2024では70件、ECTC2025でも50件近い発表がハイブリッド接合にフォーカスしており、全体の1/5から1/7がこのハイブリッド接合に関する発表となっています。当研究室からも、ECTC2024とECTC2025で各6件のハイブリッド接合を発表しました。世界の大学の中では最も多い発表件数であり、企業や公的研究機関などを含めても上位2-3番目に多い発表件数です。口頭発表の採択率は30%代前半であり、非常に狭き門になっています。我々は多くの企業と共同研究を展開しており、以下のハイブリッド接合研究などを行っています。

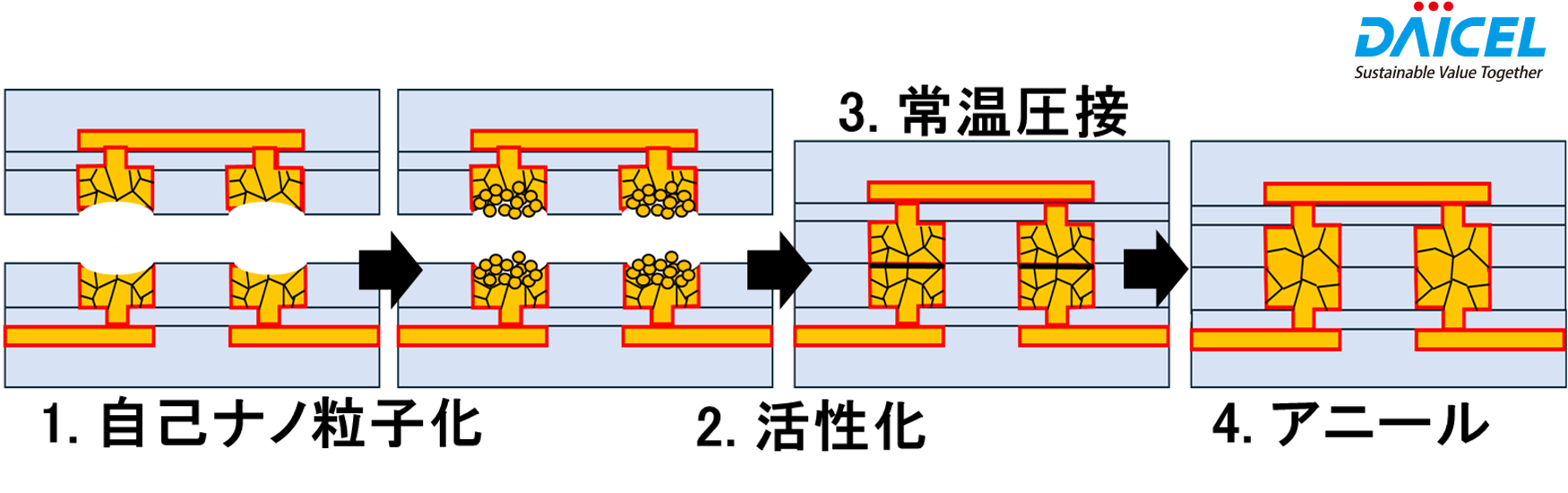

- 接合温度を下げるためにCu電極の表面をナノ粒子化する研究

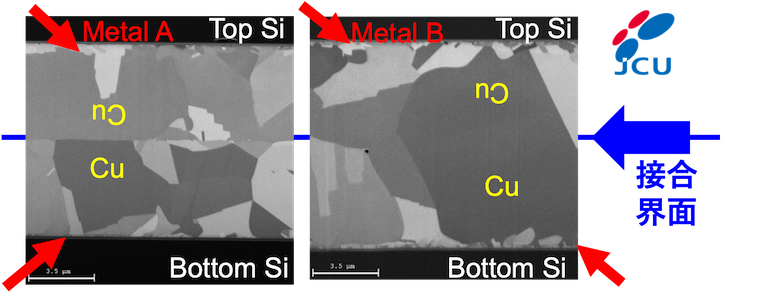

- Cuを形成する電解めっき(Cuの配向や結晶粒径)に着目した研究

- 世界最小クラス2〜3µmピッチのハイブリッド接合に関する研究

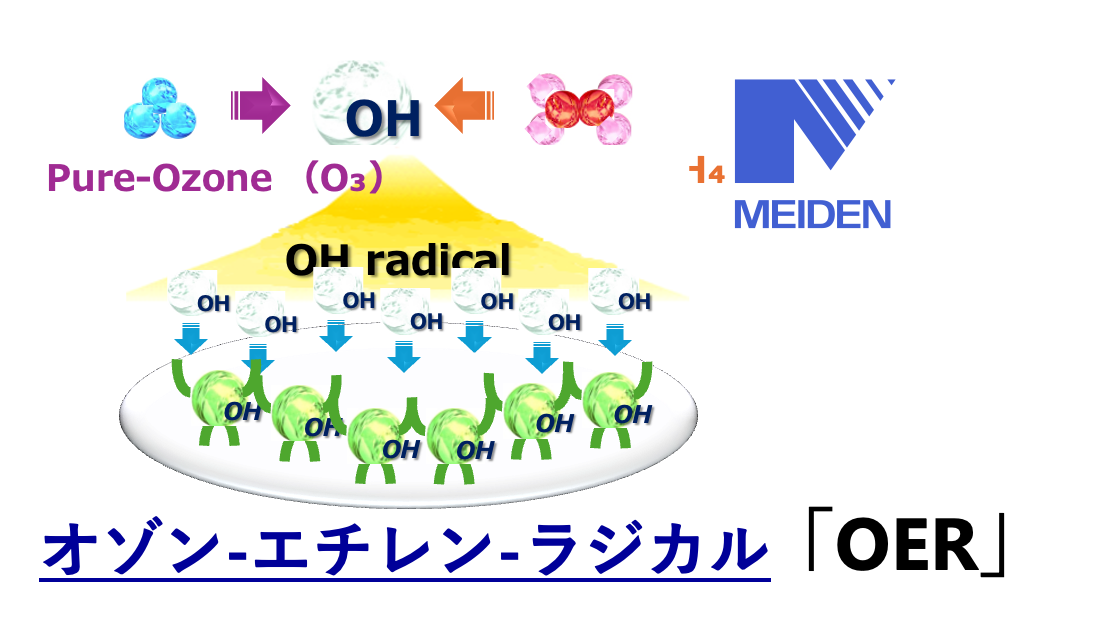

- プラズマ活性化ではなく、ダメージレスのラジカル活性化に関する研究

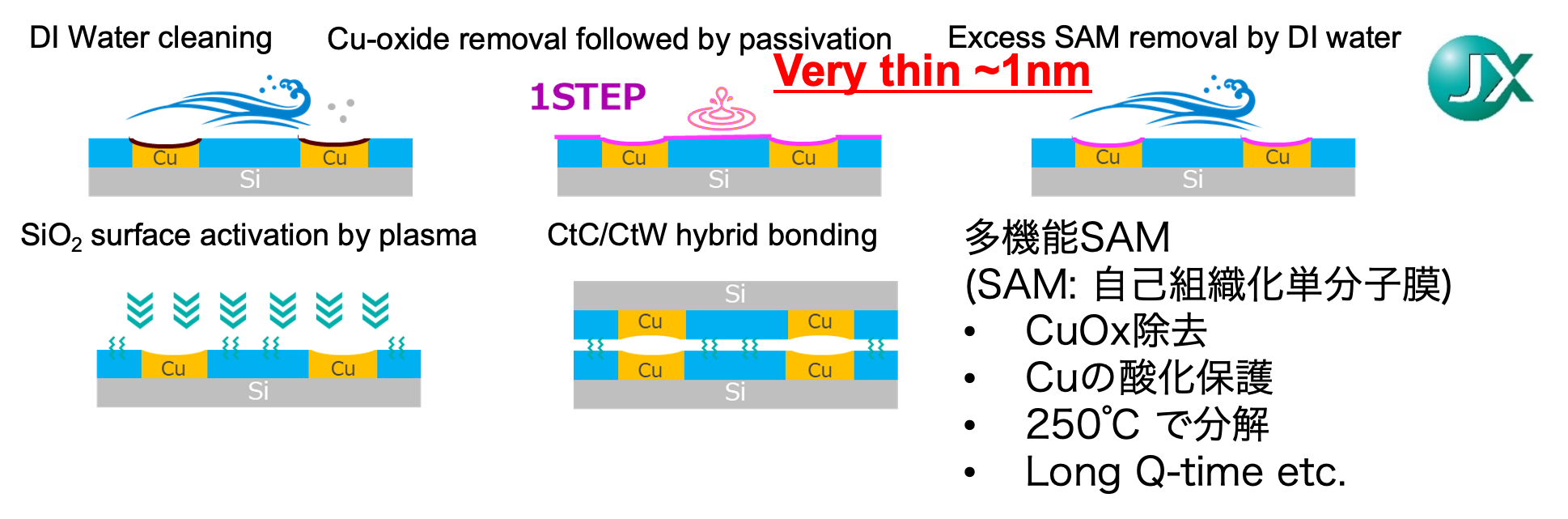

- 酸化に敏感なCuのナノ薄膜防錆技術に着目した研究

- 液滴の表面張力を駆動力としたチップの多層化とハイブリッド接合に関する研究

Cu-Cu/SiO2-SiO2ハイブリッド接合のプロセスフロー図

世界最大の半導体パッケージング技術に関する国際会議ECTCで銅と銅の原子レベル接合技術を発表

ECTC2024

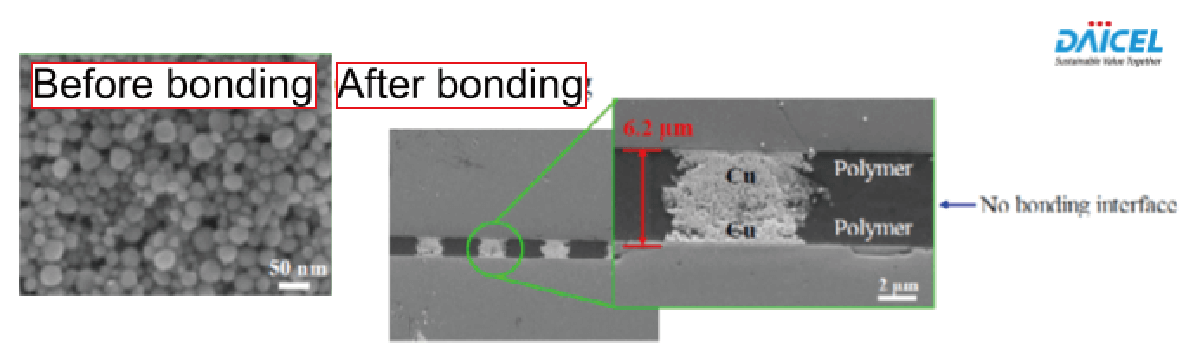

Session 21 #4 (Daicel & Tohoku): Cuペースト技術

Cuペーストと高分子絶縁膜を使ったハイブリッド接合

Session 8 #5 (Tohoku Univ. & JCU)

めっきCu下のシード層Cuのさらに下の密着層、バリア層(Under-Seed-Metal: USM)の結晶粒径や結晶構造に着目した新規Metallurgy概念を提唱

Cu-Cu/SiO2-SiO2ハイブリッド接合のX線CT写真

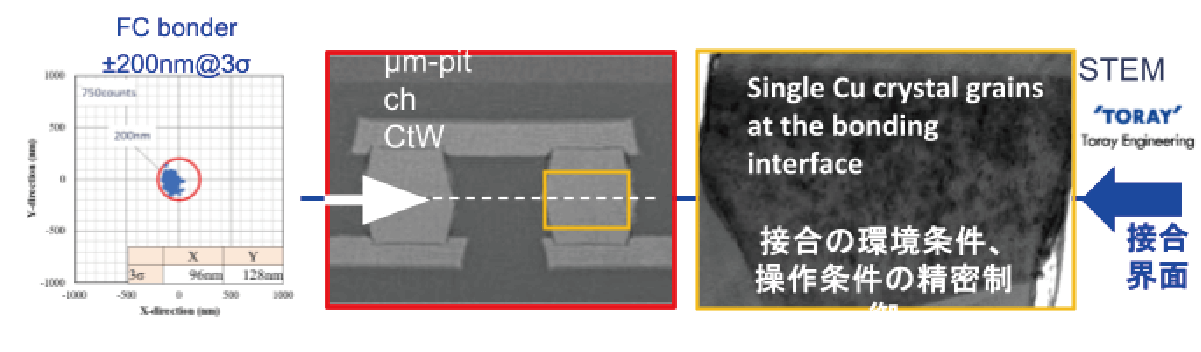

Session 10 #7 (Toray Eng., Tohoku, YNU, Univ. of Tsukuba)

3µmピッチCu-Cuハイブリッド結合

Session 40 #16 (Meiden & Tohoku Univ.)

H2Oを介した親水化接合が常識!

プラズマ活性化→ラジカル活性化

H2Oを使わず接合できる新原理提唱。信頼性向上。

Session 2 #2 (Tohoku Univ. & JX): 多機能防錆剤(CuO除去含む)

極薄ナノ機能性膜がCuの酸化を克服

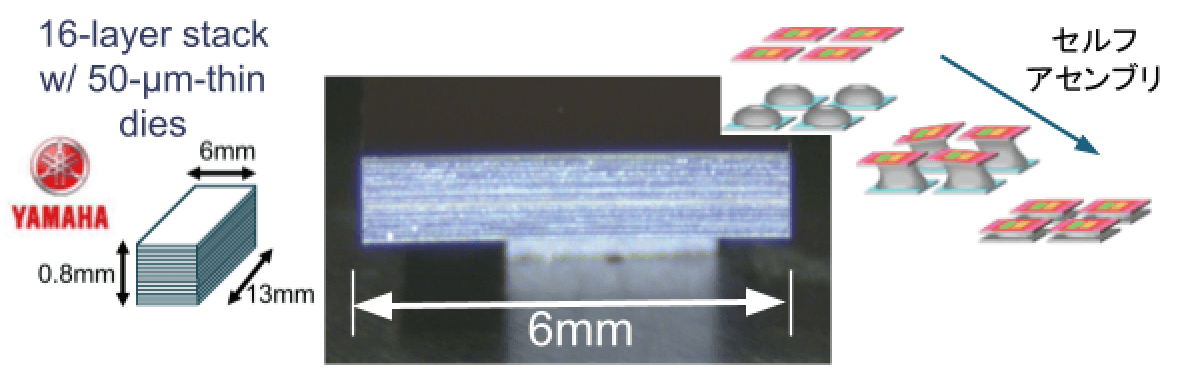

Session 32 #6 (Tohoku & Yamaha):

水の表面張力による自己組織化実装

ECTC2025

Session 8 #5 (Daicel & Tohoku Univ.): Cu pad最表層のNanoparticulation技術

表面にCuナノ粒子やペーストを供給する方法からCu電極の最表層を錯体反応でナノ粒子化する方法に転換。低温化に成功。

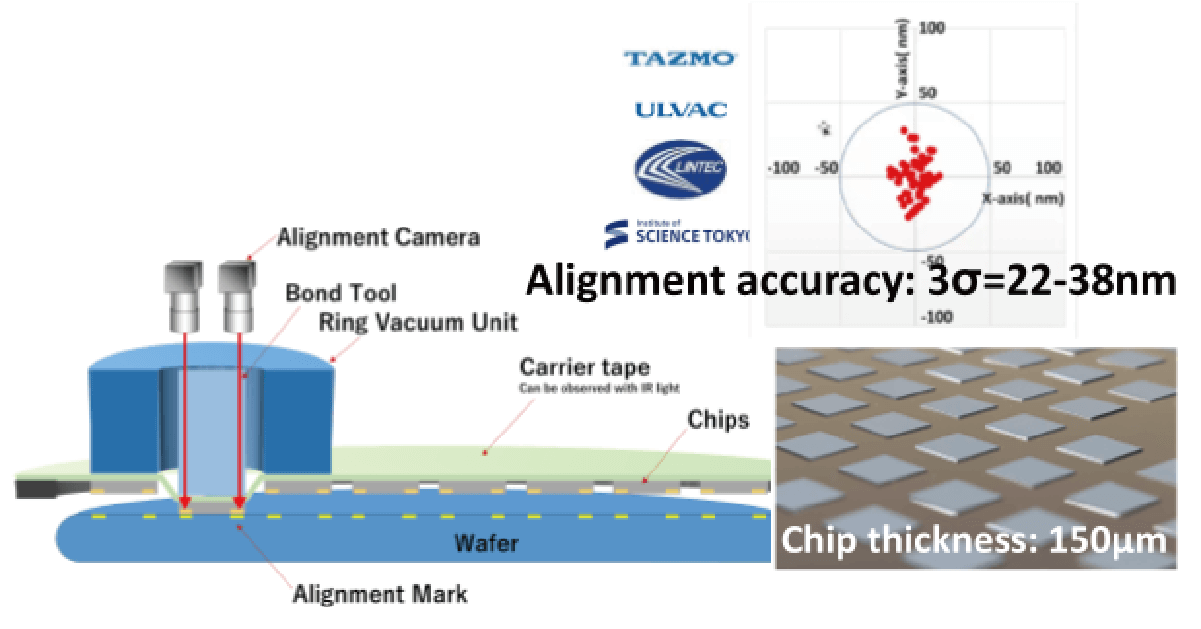

Session 8 #5 (Tazmo, Lintec, Ulvac, Tohoku Univ. & Sci. Tokyo):DBTを ⽤いた50nm@3σ⾼精度接合

Session 32 #2 (Tohoku Univ. & KEK): SATで観察できない界⾯のボイドを薄⽚加⼯無で。

変換電子収量 走査透過X線顕微鏡(CEY-STXM: Conversion Electron Yield- Scanning Transmission X-ray Microscopy)

Session 22 #3 (YNU, Torary ENG, DISCO, Tohoku Univ. & Univ. Tsukuba):Q-time評価

SiO2-SiO2接合では、プラズマ活性化後0hà2hà5hで 接合エネルギーが10%, 87%低下

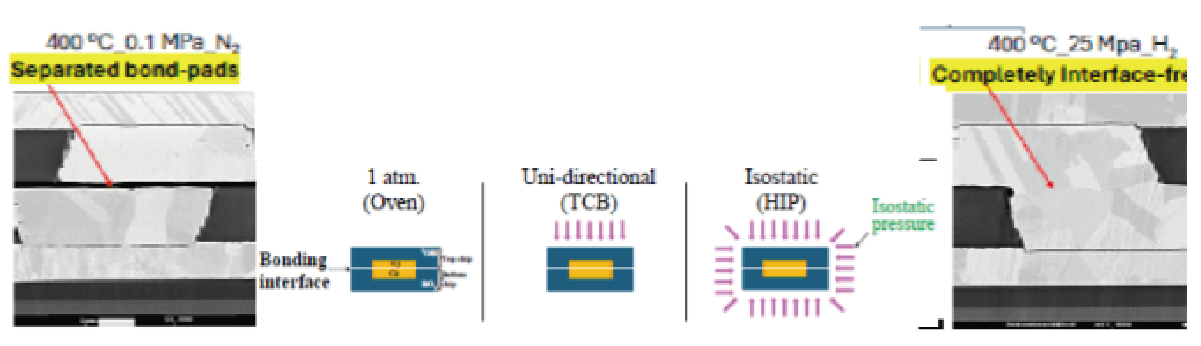

Session 39 #18 (Tohoku Univ. & KEK):Hot-Isostatic-Pressure (HIP) Annealing

熱間等方圧プレス処理を行うと、オーブンで アニールするのと同等のスループットで高歩 留り、且つ低抵抗でハイブリッド接合が可能。

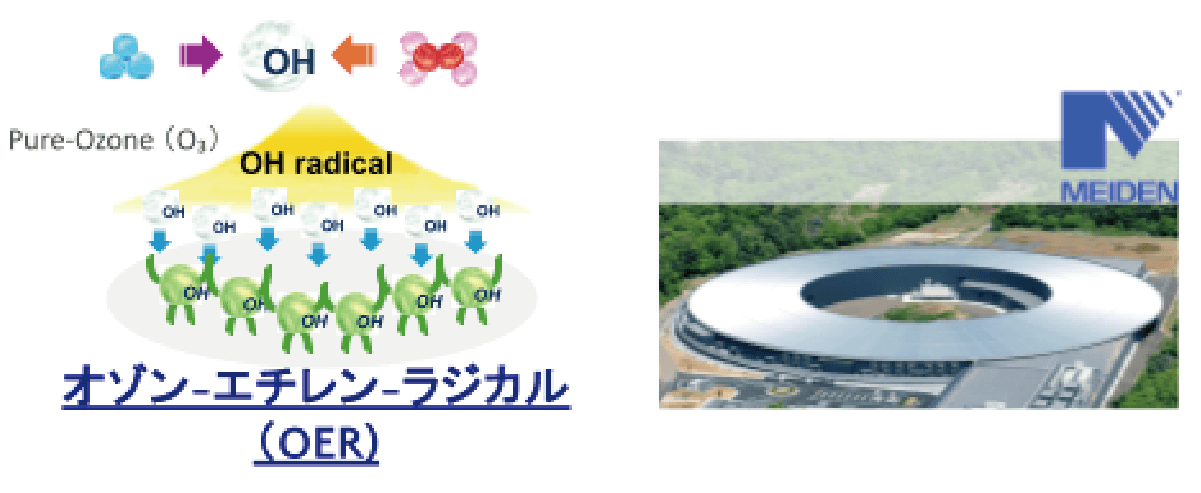

Session 39 #26 (Tohoku Univ. & Meiden):⾼輝度放射光施設NanoTerasuを活⽤

OH H2Oを介した 親水化接合が常識! プラズマ活性化 →ラジカル活性化

OER処理したSiCNの表面はSiO2より短時間で高親水性化し、Cuの表面はCu(OH)2になることを角度分解XPSより解析

Chip-to-Wafer三次元集積の一番の利点は、高いスループットと高い歩留りの両立ができる点です。Wafer-to-Wafer三次元集積は、最もスループットの高い積層方式です。チップサイズによりますが、ウエハ内には数百、数千、場合によっては数万個のチップが作り込まれているわけですが、全てのチップを一括で積層できるので、最も効率の高い方法なのです。しかし、全てのチップが良品かというと違います。例えば、ウエハによっては80%が良品チップ、20%が不良品チップの場合があります。これを2段積層すると、0.8×0.8で64%しか良品の積層チップ”3D-IC”を製造できません。これが3段積層になると、0.8×0.8×0.8で約半分が不良品となってしまうわけです。一方、Chip-to-Wafer三次元集積では、製品検査を終えて良品チップ(KGD: Known Good Die)と判定されたチップのみを選別して、ウエハ上に積層できるので、歩留りが劇的に高まります。Chip-to-Wafer三次元集積で作製された構造体は、その後、モールド、研削、メタライゼーションなどの工程をウエハの状態でプロセッシングできるので、スループットも落ちずに、高い歩留りが得られるという事になります。そのため、最近の生成AIで使われる大容量メモリHBMやGPUモジュール、スパコンなどのCPUモジュールでは、この方式が採用されています。

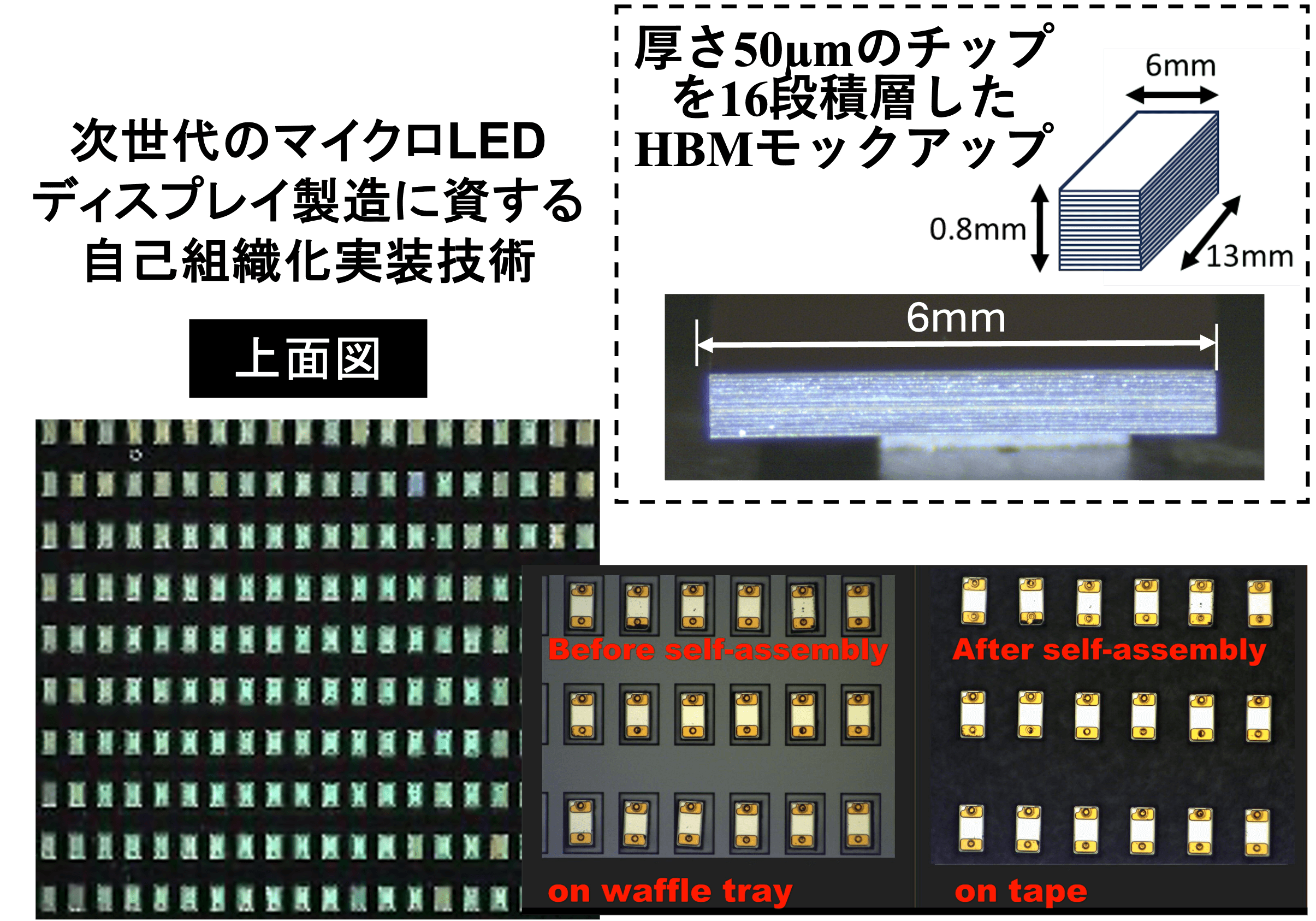

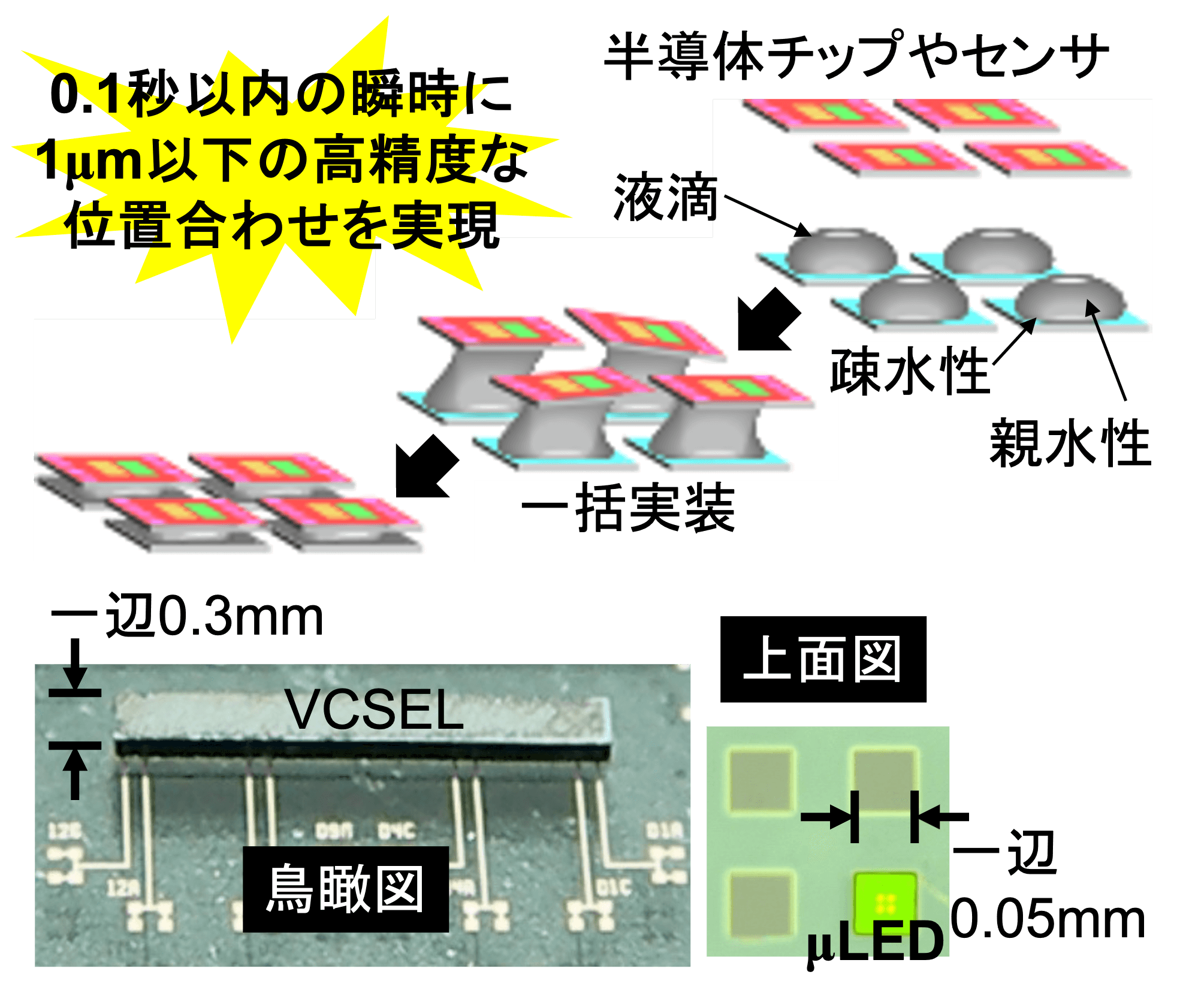

唯一の欠点は、KGDをウエハ上に搭載する工程が1つ1つの時間がかかる逐次プロセスという点です。一般的に、産業用のロボットを使ってICチップを基板に搭載する場合、高い搭載位置精度と短い搭載時間はトレードオフの関係にあります。これはICチップに限った話では無いですが、分かりやすく言うと、±1µmの高い搭載精度でICチップを実装するには、数秒以上の長い時間が必要です。逆に±10µmの低い搭載精度でICチップを実装するには1秒未満で完了します。この相反する要求特性を解決する研究も行っています。それが液滴の表面張力を駆動力とした自己組織化実装「セルフアセンブリ」です。まず、ウエハ上に親水性のチップ搭載領域を形成し、その周りに物理的、あるいは化学的な疎水領域を形成したウエハを作製します。目的の親水性領域の上に粗い精度で位置合わせし、ICチップを水滴の上に自由落下させると、水は親水性領域に閉じ込められ、表面積を最小化する方向にICチップを位置合わせする動力が作用し、高い精度で実装が可能となります。

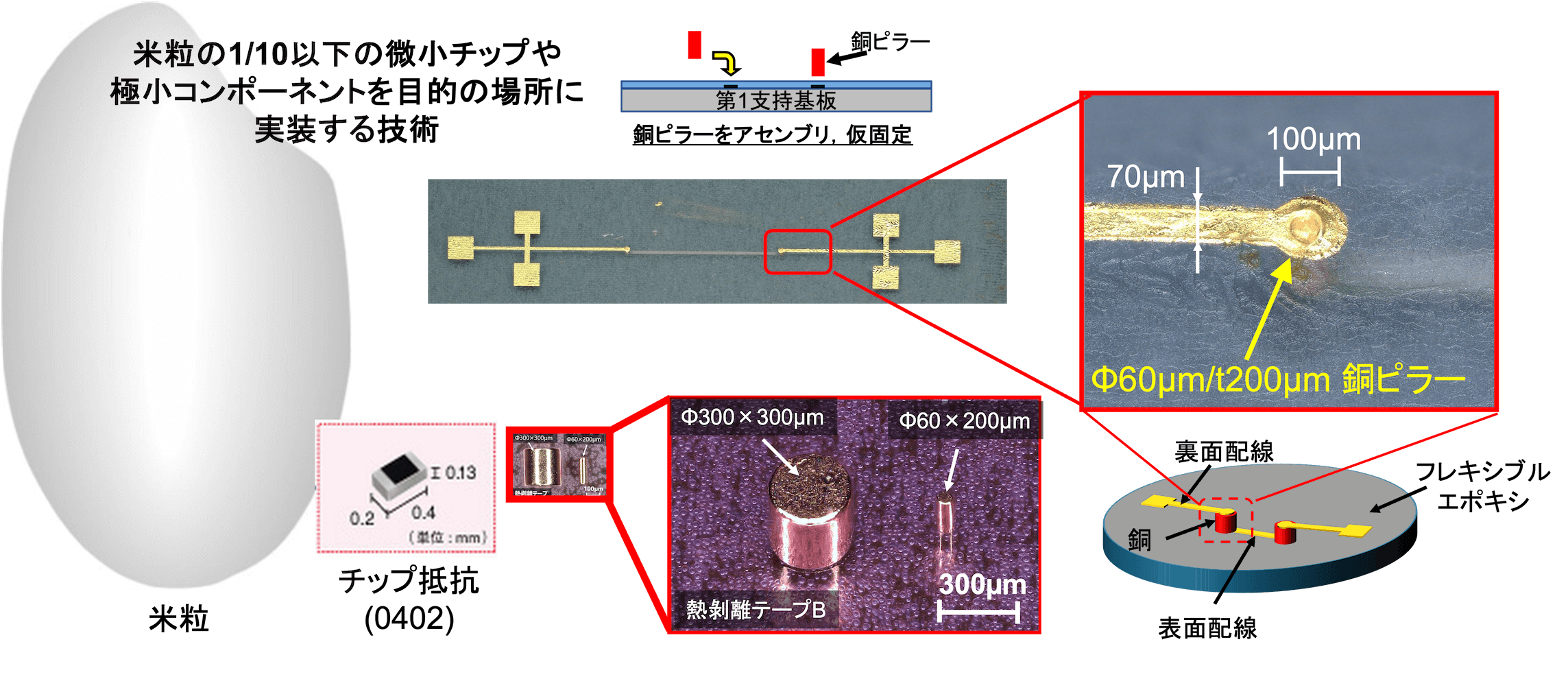

この自己組織化実装は、チップサイズが小さく、膨大な数のチップを搭載する際に効果を発揮します。これまで、一辺1mmから10mm以上のICチップのChip-to-Wafer三次元集積だけでなく、将来の光配線技術に必須となる面発光レーザーVCSELチップ(一辺0.3mm以下)や次世代ディスプレイの基幹デバイスであるµLEDチップ(一辺0.1mm以下)、さらにはアスペクト比の高い貫通配線として有用な直径60µm/高さ200µmのCuピラーをアセンブリする研究などに適用し、多数の微小コンポーネントを一括でウエハやパネルに実装するための超並列プロセスを立ち上げてきました。原理的にはリソグラフィの精度まで位置合わせ精度を高められ、チップの搭載時間を0.1秒以下に短縮できます。この自己組織化実装を使って様々なプロセス技術を研究し、実デバイスへの実用化に向けて開発を進めています。

自己組織化実装により接合した

面発光レーザーVCSEL(左)と極小LED(右)

一辺が100µm以下(髪の毛の直径が約100µm)の小構造体を高い位置合わせ精度で実装・集積

現在のマイクロピンセット方式からから量産の高速アセンブリも開発中(カイジョー社より提供)- Movie

Φ60µm、高さ200µmの微小なCu円柱をフレキシブル基板に埋め込んで貫通配線として機能化

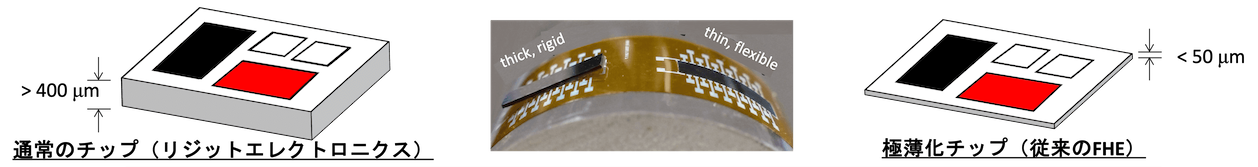

これまで3D-ICやSiインターポーザなど、主に硬い集積回路や基板の話をしてきました。ここではフレキシブルデバイスの集積化に焦点を当てた新しい研究領域「フレキシブル・ハイブリッド・エレクトロニクス(FHE)」の研究について紹介します。フレキシブル基板は、皆さんのスマホなどに必ず使われていて、硬いプリント基板の表裏をつなぐ配線として機能しています。しかし、微細化や集積化はあまり進んでいません。一方、半導体であるSi自体が硬い材料であるため、有機物で構成された半導体(有機半導体)の研究や単結晶Si自体を10µmぐらいまで極薄化して柔軟性を発現しようという試みも世の中ではなされています。しかし、有機半導体の性能は単結晶Siには全く及びません。また、単結晶Siを極薄化すると確かに曲がるのですが、変に応力をかけてしまうとトランジスタの特性が変動してしまいます。

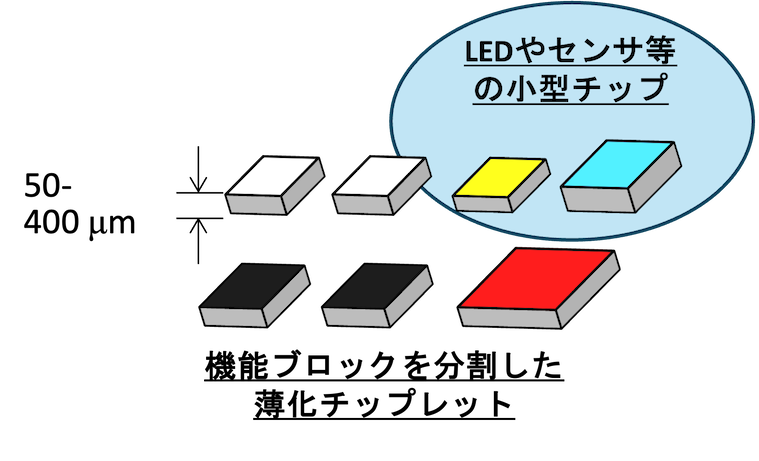

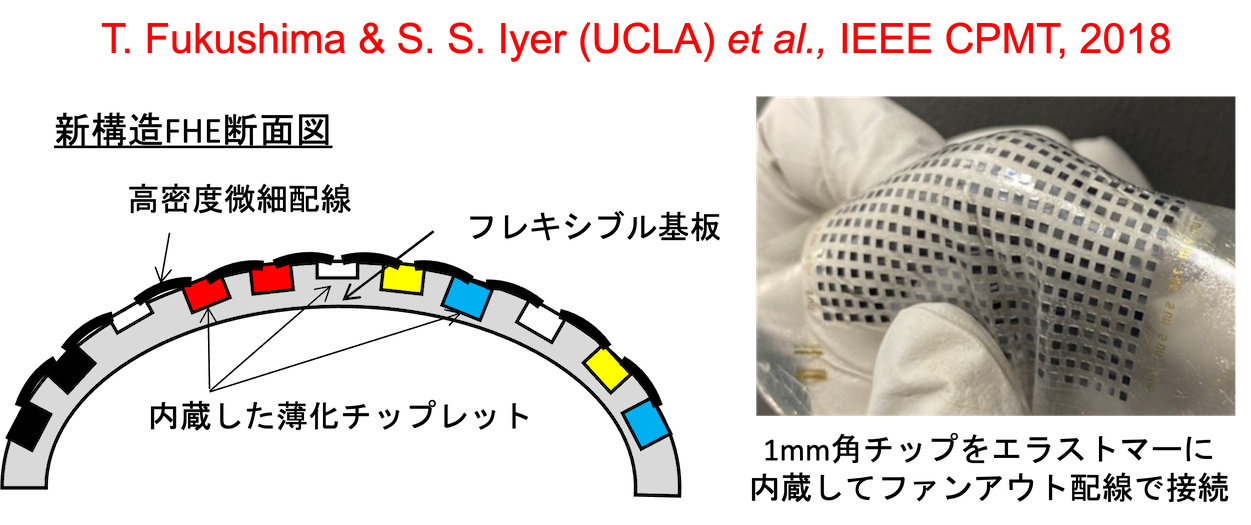

そこで我々が考えたのが「ダイレット」です。封止樹脂で覆ったり、基板に実装する前のむき出しのベアチップのことを「ダイ」と言います。このダイ(集積回路チップそのもの)を小さくして、複数の小型化ダイをアレイ状にしてフレキシブル基板に埋め込み(小さくしたダイ、これを「ダイレット」と呼びます)、先端半導体パッケージング技術を駆使して狭ピッチの微細配線で連結すると、高い柔軟性が得られます。チップ自体は特性変動を起こさないレベルに薄くしますが、チップ自体を曲げず、チップ間を結ぶ配線が曲がることによってデバイスシステム全体に高い柔軟性を付与することができました。この技術は福島が2016年に1年半留学した米国UCLAで立ち上げた研究であり、今でも学生の交流も含め、深いつながりをもってこの研究に取り組んでいます。

以下のような高集積FHEデバイス作製の実績があります。

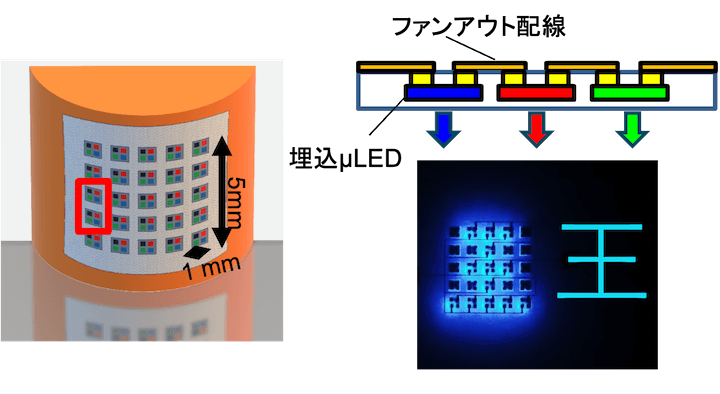

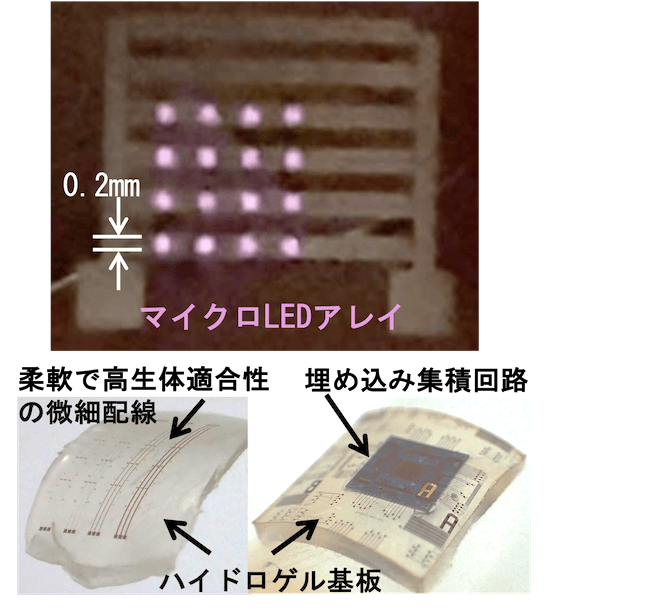

- フレキシブルµLEDディスプレイ(マイクロLEDディスプレイは次世代のディスプレイと言われており、その柔軟性を高めたデバイス)

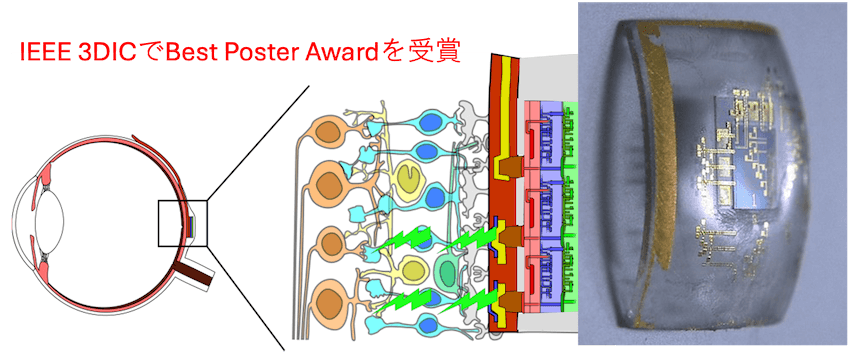

- フレキシブル人工網膜(視野角を広げるために人工網膜チップをダイレット化して柔軟な基板に内蔵させたデバイス)

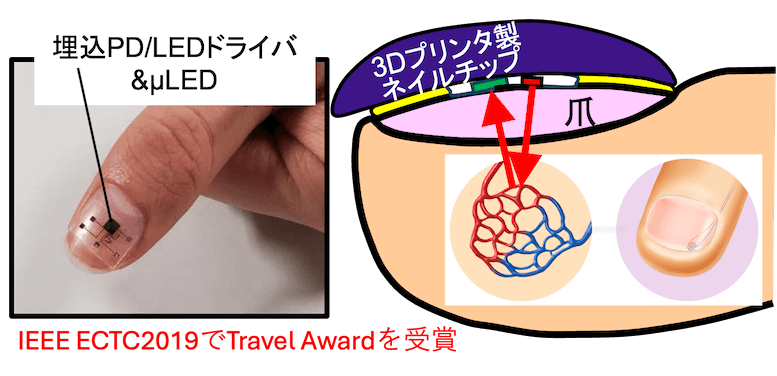

- 経爪型PPGセンサ(光電脈波PPG: Photoplethysmogramは、光を使って心拍数や血流量など生体内の情報を得る手法であり、体の中で唯一汗をかかない爪の上に実装したウエアラブルデバイス)

- コンタクトレンズ型FHE(三次元的にモールド加工したデバイスで、グルコースセンサやディスプレイとしても期待できる柔軟な三次元デバイス)

- ハイドロゲル創傷治癒デバイス(水が主成分であるハイドロゲルの中にICチップやLEDを埋め込んだり、微細配線を形成した超生体適合性の創傷治癒、歯科矯正、鬱病治療等のデバイス)

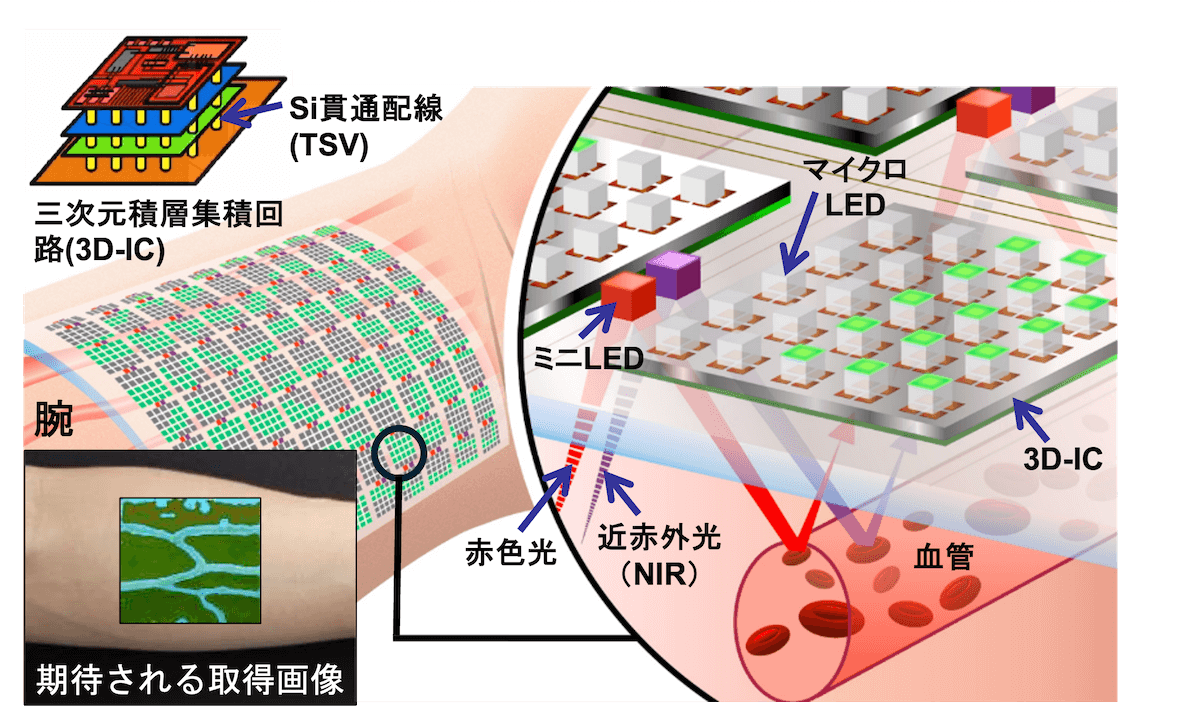

- Smart Skin Display(血管可視化シートと呼ばれ、血管の細りや血栓の予防に向け、3D-ICをダイレット化し、その上にµLEDチップのアレイを実装した健康管理デバイス)

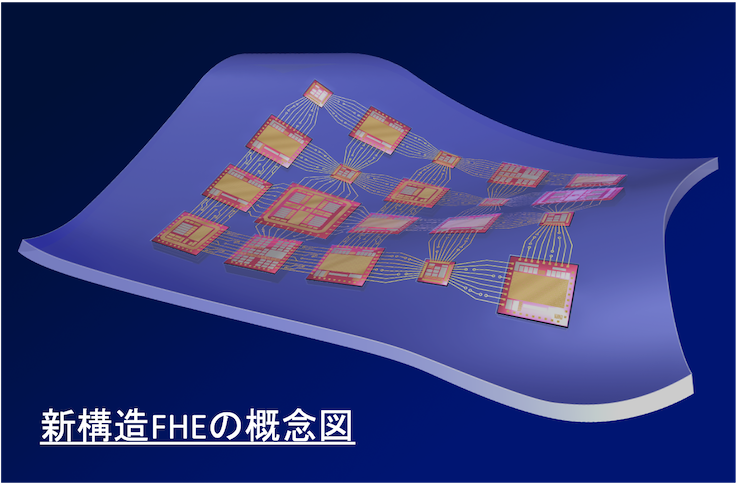

新構造FHE

- 機能ブロックを分割した小さいチップレットを使用

- 適度に薄化した硬いチップレットを内蔵(埋め込み)

- 厚さの異なるチップレットをウエハレベルで微細接続

- 無機単結晶半導体を用いた高い性能を実現

- 異種デバイス集積化フレキシブルシステムの創成

ICチップをチップレット化(小型化)し、分散してフレキシブル基板に埋め込んで集積することで高い性能と柔軟性を両立

フレキシブルµLEDディスプレイ

フレキシブル人工網膜チップ

経爪型光電容積脈波(PPG)センサ

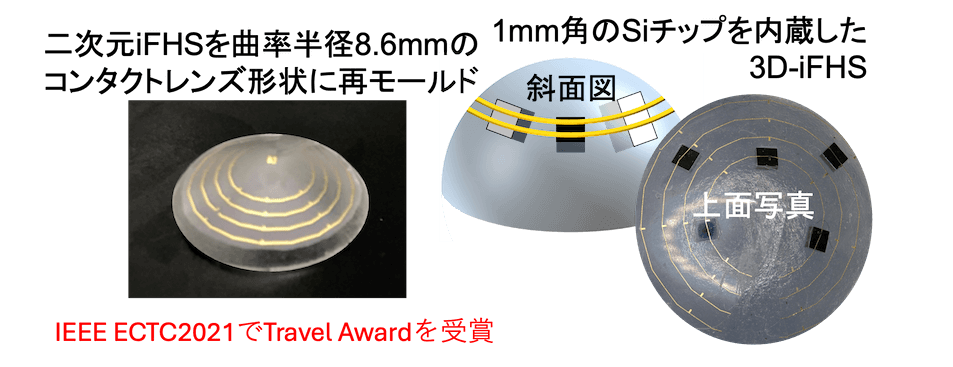

曲面集積立体iFHS

このin-Mold Flexible Hybrid Electronics (iFHE)を使った様々な応用デバイスを開発

ハイドロゲルに微細配線形成、

IC内蔵、マイクロLEDアレイ実装

低出力光療法用デバイス

(集積化フォトバイオモジュレーション)

マイクロLEDアレイを積層したウェアラブルデバイス

血管モニタリングシート (Smart Skin Display)